# ENHANCED STATE SPACE TRANSFORMATION FOR REDUCED COMPLEXITY USING HIGH-SPEED PARALLEL LINEAR FEEDBACK SHIFT REGISTER (LFSR) ARCHITECTURE

Mr.Santhosh Kumar Burugu<sup>1</sup>., G.Akshitha<sup>2</sup>

1 Assistant Professor, Department of ECE, Malla Reddy College of Engineering for Women., Maisammaguda., Medchal., TS, India 2, B.Tech ECE (19RG1A04D7), Malla Reddy College of Engineering for Women., Maisammaguda., Medchal., TS, India

## ABSTRACT

Straight criticism move registers (LFSRs) are widely applied in BCH and CRC encoders to process the rest of. An ordinary encoding plan for BCH (n, k) code work at exceptionally high recurrence and experiences the natural sequential in and sequential out restriction. At the point when the throughput of this sequential engineering can't find the framework information rate, equal preparing must be considered to meet the general prerequisites of fast correspondences and understand a higher throughput rate past gigabits every second, for example, in optical transmission. A few sorts of equal LFSR models have just been displayed in the related writing for BCH and CRC encoders. In equal CRC usage planned through numerical reasoning, tree-organized calculation and sub expressions sharing are received to improve the fell rationale parts. An improved rapid BCH encoder intended to wipe out the fan out bottleneck. This equal LFSR design is productive regarding accelerating the calculation, yet it's equipment cost is high. A sort of state-space change is created to diminish the multifaceted nature of the ordinary equal CRC circuits. By embracing direct grid change, a full speedup factor can be accomplished at the expense of an extra hardware outside the input circle. Another sort of equal LFSR dependent on IIR channel topology whose preferred position is that the pipeline procedure can be applied to accomplish some improvement in the equipment proficiency of LFSR encoders.

## INTRODUCTION

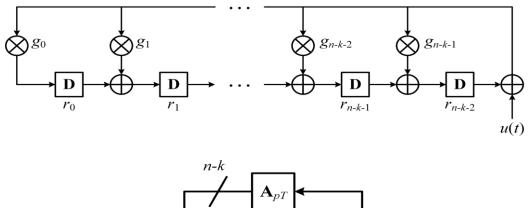

Straight input move registers (LFSRs) are widely applied in BCH and CRC encoders to register the rest of. A traditional encoding plan for BCH(n, k) code is appeared in Fig. 1. Albeit such a sequential LFSR design can work at high recurrence, it experiences the inborn sequential in and serialout constraint. At the point when the throughput of this sequential engineering can't find the framework information rate, equal preparing must be considered to meet the general prerequisites of fast interchanges furthermore, understand a higher throughput rate past gigabits every second such as in optical transmission. A few sorts of equal LFSR structures have just been displayed in the related writing for BCH and CRC encoders. In [1], an equal CRC usage has been planned through numerical reasoning. Tree-organized calculation and subexpressions sharing are received to advance the fell rationale parts. Parhi [2] and Zhang and Parhi [3] proposed an improved fast BCH encoder intended to dispense with the fanout

#### Vol.12, Issue No 4, 2022

bottleneck. This equal LFSR engineering is productive as far as accelerating the calculation, in any case, its equipment cost is high. A sort of state-space change is created in [4] and [5] to lessen the multifaceted nature of the regular equal CRC circuits. By receiving straight lattice change, a full speedup factor can be accomplished at the expense of an extra hardware outside the criticism circle. Ayinala and Parhi [6] and Jung et al. [7] proposed another sort of equal LFSR dependent on IIR channel topology what's more, its bit of leeway is that the pipeline strategy can be applied to accomplish some improvement in the equipment proficiency of LFSR encoders. Among these equal designs, Ayinala and Parhi [6] and Jung et al. [7] accomplish relatively proficient equipment usage with the circle update conditions. In state-space change, the encoder is made out of some grid duplications, with the most exertion committed to looking of change lattices that may accomplish the insignificant zone circuits. Right now, new change network development and an estimated looking through technique are proposed.

Utilizing this inexact calculation, the attractive change network can be found in an a lot shorter time than comprehensive inquiries. A low-multifaceted nature and fast equal LFSR design can be determined by applying the state-space change with the attractive arrangement. Thus, the equipment multifaceted nature can be successfully diminished without giving up execution or speed. The remainder of this brief is composed as follows. In Section II, the fundamental sequential and equal LFSR structures are looked into quickly. State-space change and IIR-based designs are referenced as two run of the mill equal plans. Segment III presents the strategy to build the changed change grid, and the comparing looking calculations for the alluring change grid are portrayed in Section IV. Segment V gives the exploratory results and makes a correlation. Ends are drawn in Section VI.

#### **Related Work:**

The change lattice utilized in [4] is picked with the end goal that lattice ApT is a friend framework, which will disentangle the criticism circle of the equal engineering. Shockingly, when Ap is changed into a buddy network ApT, lattice T and BpT may become muddled and thick with a huge number. Indeed, even the criticism circle is quick and of low intricacy true to form; different pieces of the encoder may have a more drawn out basic way with high unpredictability. After applying pipelining and retiming procedures to decrease the basic way, the information way timing is as yet not fulfilling and brings extra equipment cost too.

Then again, the  $(n-k)\times(n-k)$  lattice T has  $2(n-k)\times(n-k)$  potential outcomes, however the vector b1 has just 2n-k prospects. This distinction shows that lone a minority of potential outcomes of T are considered if utilizing b1 to create T. The change framework gotten from ideal b1 may not be the ideal one among all the conceivable outcomes of T.

Since there are different sorts of frameworks that may change the circuits into progressively productive plans, a few endeavors can be given to improve the strategy for developing grid T and to additionally streamline the equipment executions with state-space changes.

So as to locate a superior change grid, a few imperatives need to be characterized here. To begin with, the change framework T must be reversible to make the state-space change useful. Second, the all out number of 1s in networks T, ApT, and BpT ought to be as little as could be allowed. The quantity of 1s in these grids decides the quantity of XOR entryways of the encoder legitimately.

#### **Basic Searching Algorithm:**

Six CRC or BCH codes are referenced here as models. Their generator polynomials are recorded in Table I. So as to discover the alluring change lattice T, a comprehensive inquiry is performed in the vector space

of b2. The equal level p or the information size is picked as the level of generator polynomials for a reasonable examination with past designs. The proposed technique can be applied at any equal level.

Since the lattices T, ApT, and BpT really suggest the association of the coupling circuits, it follows that the equipment intricacy is identified with the all out number of 1s in these three networks, which is meant as TN in the accompanying. Therefore, we are keen on finding a b2 that limits TN.

The fundamental looking through calculation we utilized is as per the following. To begin with, the coupling grids An and Bp can be processed for each of the generator polynomials in Table I with input size p = n - k. At that point we cross all the potential estimations of b2 to develop change lattice T, and subject it to (5) to acquire changed coupling grids Well-suited and BpT . A short time later, the TN is tallied. Minimal one here shows the most reduced multifaceted nature of equipment, and the comparing vector b2 is viewed as the best arrangement meant as  $b \ge 2$ . At the point when n - k = 12 or n - k = 16, our looking through calculation is all around qualified to discover b\*2in a sensible time. The outcomes are recorded in Table II as far as the arrangement of the vectors (b\* 2) (spoke to in hexadecimal), the quantity of 1s, the quantity of the XOR entryways utilized in equipment circuits (XOR), and the basic way delay (CPD) (in wording of XOR entryways). On the other hand, Table II additionally records the vectors (b\* 1) used to develop the change networks by the technique depicted in [4]. Their point by point looking through calculation can be found in [5]. It ought to be noticed that TN is viewed as the quantity of XOR doors straightforwardly in [5]. Notwithstanding, in our investigation, the genuine number of XOR entryways is not as much as TN by receiving the subexpressions sharing system. For instance, if there are four 1s shaping a square shape in network T (Well-suited or BpT), one XOR is required for the network calculation rather than 2. Table II replaces the first number of XOR entryways recorded in [5] with the outcomes we figured. We can see that the aggregate number of XOR entryways utilizing the proposed change network is littler than the outcomes in [5], while the CPD essentially remains the same.

Be that as it may, for n - k = at least 32, the vector space of b2 is too huge and this thorough looking through calculation requires more than one month to acquire the outcomes. This limits the application of this looking calculation for high-request generator polynomials. An option looking through calculation is proposed beside acquire the wanted change network all the more rapidly.

## **Designing Work:**

## **Router Architecture:**

The Four Router Design is finished by utilizing of the three squares. The squares are 8-Bit Register, Router controller and yield square. the switch controller is configuration by utilizing FSM structure and the yield square comprises of three fifo's consolidated together the fifo's are store bundle of information and when u need to information that time the information read from the FIFO's. In this switch configuration has three yields that is 8-Bit size and one 8\_bit information port it utilizing to drive the information into switch we are utilizing the worldwide clock and reset signals, and the blunder signal and suspended information sign are yields of the switch .the FSM controller gives the fail and suspended\_data\_in signals.this capacities are talked about obviously in beneath FSM portrayal.

Vol.12, Issue No 4, 2022

**Result Outputs:**

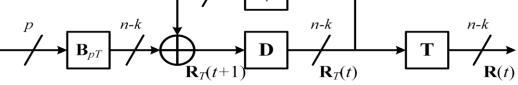

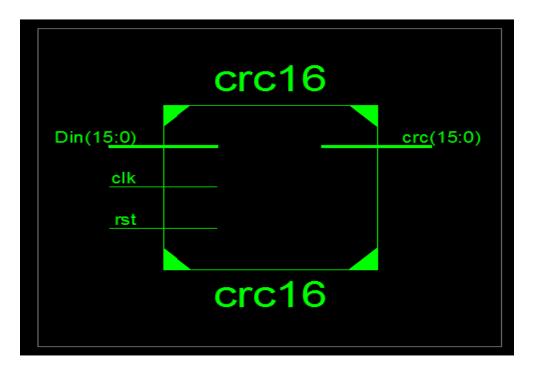

Rtl

## Vol.12, Issue No 4, 2022

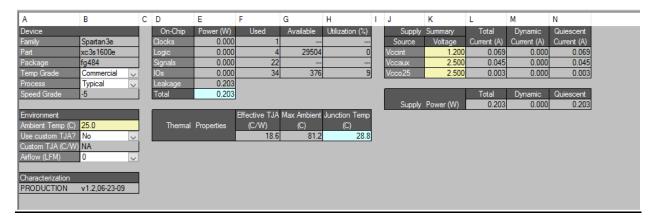

| Device Utilization Summary                     |      |           |             |         |  |  |  |  |

|------------------------------------------------|------|-----------|-------------|---------|--|--|--|--|

| Logic Utilization                              | Used | Available | Utilization | Note(s) |  |  |  |  |

| Number of Slice Flip Flops                     | 5    | 29,504    | 1%          |         |  |  |  |  |

| Number of 4 input LUTs                         | 4    | 29,504    | 1%          |         |  |  |  |  |

| Number of occupied Slices                      | 3    | 14,752    | 1%          |         |  |  |  |  |

| Number of Slices containing only related logic | 3    | 3         | 100%        |         |  |  |  |  |

| Number of Slices containing unrelated logic    | 0    | 3         | 0%          |         |  |  |  |  |

| Total Number of 4 input LUTs                   | 4    | 29,504    | 1%          |         |  |  |  |  |

| Number of bonded IOBs                          | 34   | 376       | 9%          |         |  |  |  |  |

| IOB Flip Flops                                 | 12   |           |             |         |  |  |  |  |

| Number of BUFGMUXs                             | 1    | 24        | 4%          |         |  |  |  |  |

| Average Fanout of Non-Clock Nets               | 1.41 |           |             |         |  |  |  |  |

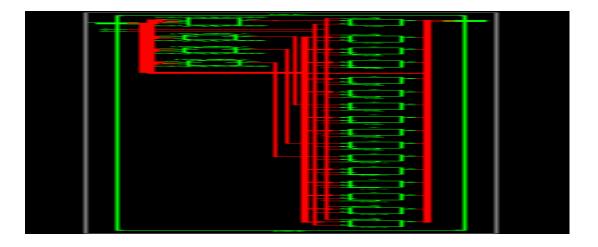

## Simulation results

|               |             |           |          |        |          |          | 1,000.000 ns |

|---------------|-------------|-----------|----------|--------|----------|----------|--------------|

| Name          | Value       | 0 ns      |          | 200 ns | 400 ns   | 600 ns   | 800 ns       |

| ▶ 號 crc[15:0] | 00000110001 | (1100000) | 1111100  | *      | 00000110 | 00111011 |              |

| 🔚 clk         | 1           |           |          |        |          |          |              |

| 1🐻 rst        | 0           |           |          |        |          |          |              |

| 🕨 📷 Din[15:0] | 00000000011 | 0000000)  | 11111111 | k      | 0000000  | 01111011 |              |

|               |             |           |          |        |          |          |              |

|               |             |           |          |        |          |          |              |

#### CONCLUSION

This brief has proposed a new method to construct the transformation matrix used in the state-space transformation. A timesaving searching algorithm has been presented for searching of a good transformation matrix as well. Based on this improved statespace transformation, reduced-complexity parallel architectures can be obtained. Experimental results have shown that the proposed architecture outperforms the previous designs for high-speed implementation of BCH or CRC encoders.

#### REFERENCES

[1] T.-B. Pei and C. Zukowski, "High-speed parallel CRC circuits in VLSI," *IEEE Trans. Commun.*, vol. 40, no. 4, pp. 653–657, Apr. 1992.

[2] K. K. Parhi, "Eliminating the fanout bottleneck in parallel long BCH encoders," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 51, no. 3, pp. 512–516, Mar. 2004.

[3] X. Zhang and K. K. Parhi, "High-speed architectures for parallel long BCH encoders," in *Proc. ACM Great Lakes Symp. VLSI*, Boston, MA, USA, Apr. 2004, pp. 1–6.

[4] J. H. Derby, "High-speed CRC computation using state-space transformations," in *Proc. IEEE GLOBECOM*, Nov. 2001, pp. 166–170.

[5] C. Kennedy and A. Reyhani-Masoleh, "High-speed CRC computationsusing improved state-space transformations," in *Proc. IEEE Int. Conf. Electro/Inf. Technol.*, Jun. 2009, pp. 9–14.

[6] M. Ayinala and K. K. Parhi, "High-speed parallel architectures for linear feedback shift registers," *IEEE Trans. Signal Process.*, vol. 59, no. 9,pp. 4459–4469, Sep. 2011.

[7] J. Jung, H. Yoo, Y. Lee, and I.-C. Park, "Efficient parallel architecture for linear feedback shift registers," *IEEE Trans. Circuits Syst. II, Express Briefs*, vol. 62, no. 11, pp. 1068–1072, Nov. 2015.